|

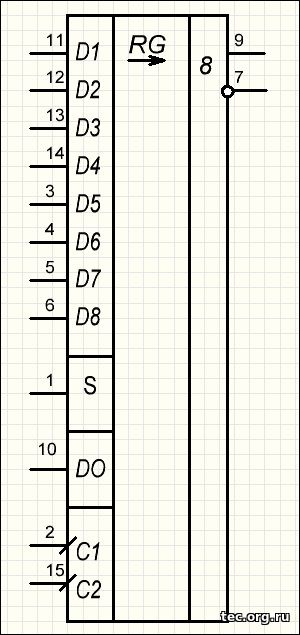

Микросхема КР1533ИР9 имеет вход последовательных данных D0, восемь входов параллельной загрузки D1-D8, прямой и инверсные выходы OUT, два равноправных тактовых входа C1 и C2 и синхронный вход разрешения параллельной загрузки S.

Установка т.е. параллельная загрузка информации в регистр со входов D1-D8 происходит при низком уровне напряжения на входе S синхронно с положительным фронтом синхроимпульса на любом входе C.

Сдвиг данных от младших разрядов к старшим происходит синхронно с синхроимпульсами на любом из входов С. При этом в первый разряд загружается информация со входа D0.

Хранение. При высоких уровнях напряжения на входах C1, C2 состояние регистра не меняется.

* В ряде источников один из входов C называется входом блокировки синхросигнала. На самом деле, входы объединены логикой ИЛИ - все равно на какой из них подавать тактовый сигнал, другой вход должен быть при этом иметь низкий логический уровень либо должен быть объединен с первым. При высоком постоянном уровне на одном их входов C регистр переходит в режим хранения (т.е. синхросигнал блокируется).

|