|

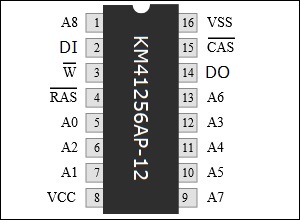

Корпус: DIP-16

- Организация 262144 х 1 бит

- ТТЛ-совместимые уровни сигналов.

- Выход данных с тремя состояниями

- Регенерация 256 циклов за 4mS

- Чтение, Запись, Чтение-модификация-запись

- RAS-only регенерация, скрытая регенерация

- Режимы страничного чтения и записи

- Режим ранней записи

|

Микросхема KM41256AP-12 представляет собой динамическое ОЗУ, имеющее организацию: 256K слов по 1 биту (матрица 512x512 ячеек хранения данных).

Основные параметры KM41256AP-12:

| Uпит.раб. |

4,5..5,5V

|

|

Ток потребления:

В рабочем режиме

В режиме Standby

|

< 75mА

< 4,5mА

|

|

Входное напряжение:

низкого уровня

высокого уровня

|

<0,8V

>2,4V |

|

Выходное напряжение:

низкого уровня

высокого уровня

|

<0,4V

>2,4V

|

|

Выходной ток:

низкого уровня

высокого уровня

|

не менее:

4,2mА

5,0mА

|

|

Время выборки Trac:

|

<120nS

|

| Время рабочего цикла |

<230nS |

| Корпус |

DIP-16

|

| Диапазон температур |

-10..+70°C |

| Аналог |

~КР565РУ7В

(примерный) |

|

|

Накопитель ЗУ организован в виде матрицы, содержащей 512 строк и 512 столбцов. Кроме того, в состав накопителя входят две сдвоенные четвёрки резервных строк и четыре пары резервных столбцов, всего 8 256 резервных ячеек.

Схема управления ЗУ состоит из двух генераторов тактовых сигналов, которые включаются сигналами RAS# (строб адреса строки) и CAS# (строб адреса столбца). Для выборки любой из ячеек памяти требуется 18-разрядный код, подаваемый на 9-разрядный адресный регистр в мультиплексном режиме - сперва в параллельном коде подаётся младшие девять разрядов адреса, которые служат для выборки нужной строки, код адреса строки фиксируется на адресном регистре при помощи сигнала RAS# тогда, когда тот переходит на нижний логический уровень, затем на те же выводы подаётся девять старших разрядов кода адреса, соответствующих адресу столбца, код адреса столбца фиксируется на адресном регистре при помощи второго синхронизирующего сигнала, CAS#.

|

Таблица функционирования KM41256AP-12:

| Входы |

Код адреса

|

Вход |

Выход |

Режим |

|

___

RAS

|

___

CAS

|

__

WR

|

(A0-A8)

|

DI |

DO |

| 1 |

1 |

0 |

X |

X |

Z |

Хранение |

| 1 |

0 |

1 |

X |

X |

Z |

Хранение |

| 0 |

1 |

X |

перебор

адресов |

X |

Z |

Регенерация |

| 0 |

0 |

X |

X |

D |

Z |

Запись D |

| 0 |

0 |

1 |

|

Z |

D |

Считывание D |

0 - низкий уровень, 1 - высокий уровень,

Z - высокоимпедансное состояние.

X - произвольное состояние

|