|

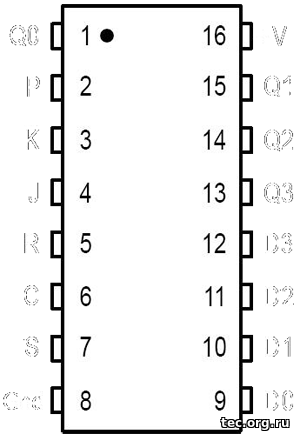

Корпус: DIP-16

|

Микросхема К561ИР9 представляет собой четырёхразрядный сдвиговый регистр.

Основные параметры К561ИР9:

| Uпит.раб. |

3-15V

|

| Uпит.max. |

18V |

| Ток потребления |

<20мкА |

| Уровни сигналов |

КМОП

(CD40xx/К561)

|

| Корпус |

DIP-16 |

| Максимальная частота (при Uп=15В) |

3МГц |

| Время задержки распространения |

650-800нс (5В)

235-360нс(10В) |

| Длительность тактового импульса |

>250нс |

| Длительность импульса сброса |

>200нс |

| Выходной ток низкого уровня |

0,35мА (Uп=5В)

0,85мА(Uп=10В) |

| Выходной ток высокого уровня |

0,25мА (Uп=5В)

0,6мА(Uп=10В) |

| Диапазон температур |

-10..+70°C |

| Аналог |

CD4035 |

Входные и выходные уровни сигналов зависят от напряжения питания и, в общем случае, соответствуют таковым у других микросхем серий КМОП-логики.

|

|

Микросхема К561ИР9 - четырехразрядный сдвигающий регистр на D-триггерах. Она позволяет осуществлять параллельную и последовательную загрузку, а также параллельное и последовательное считывание в любых сочетаниях.

ИС К561ИР9 имеет четыре выхода (Q0-Q3) и следующие входы:

- вход сброса R,

- вход для подачи тактовых импульсов С,

- вход выбора режима S (параллельно/последовательно),

- вход выбора "полярности" выходного сигнала Р,

- входы последовательной записи J и К

- входы параллельной записи D0-D3.

Вход R является асинхронным - при подаче на него лог.1 независимо от состояния других входов все триггеры микросхемы устанавливаются в 0. Если на входе R лог.0, возможна запись информации в триггеры микросхемы.

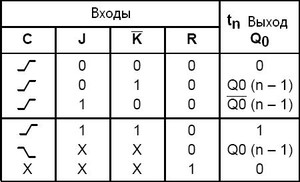

При лог.1 на входе выбора режима S по спаду импульса отрицательной полярности на входе С произойдет параллельная запись информации в триггеры регистра со входов D0-D3. Если на входе S лог.0, по спаду импульса отрицательной полярности на входе С произойдет запись информации со входов J и К в триггер с выходом D0 и сдвиг информации в остальных триггерах в сторону возрастания номеров выходов. Информация, которая будет записана в первый триггер, определяется состоянием входов J и К перед подачей спада импульса отрицательной полярности на вход С. Если объединить между собой входы J и К, будет производиться запись информации, имеющейся на этих объединенных входах (это будет аналогом D-входа). Если на вxoд J подать лог. 0, на вход К - лог. 1, изменения информации в первом триггере по спаду импульса отрицательной полярности на входе С не произойдет. При лог. 1 на входе J и лог. 0 на входе К первый триггер микросхемы переходит в счетный режим и меняет свое состояние на противоположное на каждый спад импульса отрицательной полярности на входе С.

Полярностью сигналов на выходах 1-4 регистра можно управлять подачей управляющего сигнала на вход Р - при лог. 1 на этом входе выходные сигналы выдаются в прямом коде, при лог. 0 - инвертируются.

|

|

Условное обозначение К561ИР9:

|

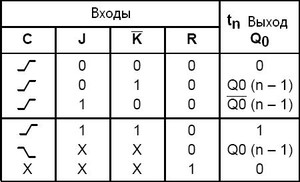

Таблица функционирования К561ИР9:

(Последовательный режим: P=1, S=0)

0 - низкий уровень, 1- высокий уровень,

X - произвольное состояние.

|