|

Корпус: DIP-24W

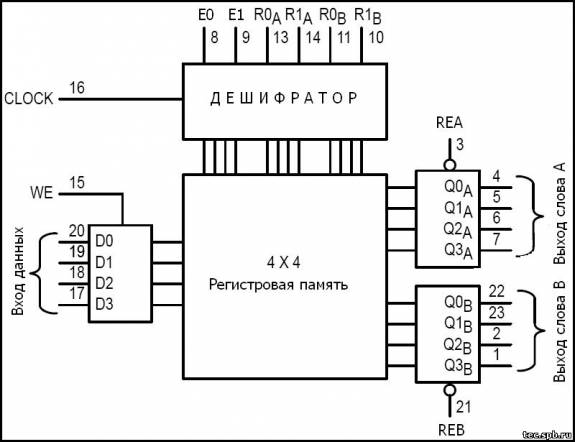

Микросхема К561ИР12 содержит регистровую память 4х4, дешифратор записи адреса, два отдельных дешифратора считывания адресов и две выходных шины с Z-состоянием, которые упрощают присоединение устройства к системам с шинной организацией.

Четырёхразрядная входная шина (D0-D3) одинарная, выходная шина двойная - слово А и слово B (Q0-Q3). Считывание данных из регистров на выходные шины A и B независимое, запись со входа также независимая.

Если на входе разрешения записи WE высокий уровень то запись четырёхразрядного слова происходит по адресу, заданному на адресных входах E0, E1, по фронту импульса на тактовом входе C. При низком уровне на входе WE данные со входов D0-D3 не воспринимаются.

Считывание информации на выходы A и B происходит по фронту тактового импульса только в том случае, если на входах REA и REB соответственно установлены высокие уровни сигналов. При низких уровнях сигналов на этих входах выходы A и B переводятся в Z-состояние. Адреса считываемых слов задаются входами R0A, R1A и R0B, R1B для выходов A и B соответственно.

Запись четырёхразрядного слова в произвольную ячейку микросхемы К561ИР12 и считывание двух других произвольных ячеек на выходные шины An и Bn может происходить одновременно, что позволяет строить устройства памяти с высокой скоростью доступа.

|

Микросхема К561ИР12А представляет собой многопортовый регистр 4х4 бит.

Основные параметры К561ИР12А:

(при t=+25°C)

| Параметр |

Min |

Max |

| Uпит. |

3В

|

15В |

|

Ток потребления статический:

при Uпит=5В

при Uпит=10В

|

|

10мкА

100мкА |

|

Входной ток низкого/высокого уровня

|

|

±0,05мкА |

|

Выходное напряжение низкого уровня

|

|

0,01В |

| Выходное напряжение высокого уровня |

Uпит-0,01В |

|

|

Выходной ток:

низкого уровня:

при Uпит=5В Uвых=0,4В

при Uпит=10В Uвых=0,5В

|

0,2мА

0,5мА

|

|

Выходной ток: высокого уровня:

при Uпит=5В Uвых=2,5В

при Uпит=10В Uвых=9,5В |

0,2мА

|

|

|

Ток утечки в Z-состоянии

|

|

10мкА |

|

Время задержки распространения сигнала при включении:

Uпит=5В, Cвых=50пФ

Uпит=10В, Cвых=50пФ

|

|

5500нс

2100нс

|

| Тактовая частота |

|

5МГц |

| Длительность тактового импульса |

60нс |

|

| Корпус |

239.24-1

(DIP-24W)

|

| Диапазон температур |

-10..+70°C |

| Аналог |

MC14580B

|

|

|

Расположение выводов К561ИР12:

Входные и выходные уровни сигналов зависят от напряжения питания и, в общем случае, соответствуют таковым у других микросхем серий КМОП-логики.

|

Назначение выводов К561ИР12:

|

1

|

Q3B |

Выход

|

|

2

|

Q2B |

|

|

3

|

REA |

|

|

4

|

Q0A |

|

|

5

|

Q1A |

|

|

6

|

Q2A |

|

|

7

|

Q3A |

|

|

8

|

E0 |

Вход адреса записи

|

| 9 |

E1 |

Вход адреса записи

|

| 10 |

R1B |

Вход адреса считывания

|

| 11 |

R0B |

Вход адреса считывания

|

| 12 |

GND |

Общий |

| 13 |

R0A |

Вход адреса считывания |

|

14

|

R0B

|

Вход адреса считывания |

| 15 |

WE |

Вход разрешения записи |

| 16 |

C |

Тактовый вход |

| 17 |

D3 |

Вход информационный |

| 18 |

D2 |

Вход информационный |

| 19 |

D1 |

Вход информационный |

| 20 |

D0 |

Вход информационный |

| 21 |

REB |

Разрешение выхода B |

| 22 |

Q0B |

Выход |

| 23 |

Q1B |

Выход |

| 24 |

+U |

Питание |

|

|

Таблица функционирования микросхемы К561ИР12

( п р и м е р ы р а б о т ы )

| Входы |

Выходы |

Режим

работы

|

| C |

WE |

E1 |

E0 |

R1A |

R0A |

R1B |

R0B |

REA |

REB |

Dn |

QnA |

QnB |

|

1 |

A1 |

A2 |

A1 |

A2 |

A1 |

A2 |

1 |

1 |

1 |

1 |

1 |

Запись и считывание по одному адресу одновременно |

|

1 |

A1 |

A2 |

A1 |

A2 |

A1 |

A2 |

1 |

1 |

0 |

0 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

X |

Не изменяется |

Не изменяется |

Х

Р

А

Н

Е

Н

И

Е

|

| X |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

X |

Z |

Z |

| 0 |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

X |

Не изменяется |

Не изменяется |

| 1 |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

X |

Не изменяется |

Не изменяется |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

Записывается по адресу 00 |

Слово с адреса 01 |

Слово с адреса 10 |

Запись и считывание по разным адресам одновременно |

|

0 |

X |

X |

0 |

1 |

1 |

0 |

1 |

1 |

X

(Запись не происходит)

|

Слово с адреса 01 |

Слово с адреса 10 |

Считывание двух разных адресов на два выхода одновременно |

|

0 |

X |

X |

1 |

1 |

X |

X |

1 |

0 |

X

(Запись не происходит) |

Слово с адреса 11 |

Z |

Считывание одного адреса, второй выход отключен |

0 - низкий уровень, 1 - высокий уровень, X - произвольное состояние, Z - высокоимпедансное состояние, A1, A2 - произвольные биты адреса (0/1).

|