|

4096 (MMC4096E)

| Распродажа | |

04.09.2017, 00:04:43 |

| ЦЕНА розничная: 15руб | от 10шт: 10руб | от 100шт: 5руб |

|

Корпус: DIP-14

Входные и выходные уровни сигналов зависят от напряжения питания и, в общем случае, соответствуют таковым у других микросхем серий КМОП-логики.

|

Микросхема MMC4096E представляет собой JK-триггер типа Master-slave с дополнительной логикой на входах.

Основные параметры MMC4096E:

| Uпит.раб. |

3-15V

|

| Uпит.max. |

18V |

| Ток потребления |

<0,08мА |

| Уровни сигналов |

КМОП

(CD40xx/К561)

|

Максимальная частота, не менее:

при Uп=5V

при Uп=10V

при Uп=15V |

3,5MHz

8,0MHz

12,0MHz |

Длительность тактового импульса, не менее:

при Uп=5V

при Uп=10V

при Uп=15V |

140nS

60nS

40nS |

| Выходное напряжение лог.0 |

<0,05V |

| Выходное напряжение лог.1 |

>Uпит-0,05V |

Выходной ток низкого/высокого уровня:

при Uпит=5V

при Uпит=15V |

1mA

6,8mA |

| Входной ток |

<0,3µA |

| Входная ёмкость |

<7.5pF |

| Диапазон температур |

-40..+85°C |

| Корпус |

DIP-14 |

| Аналоги |

CD4096BE

HEF4096BP

HCF4096BEY

MC14096BP |

|

|

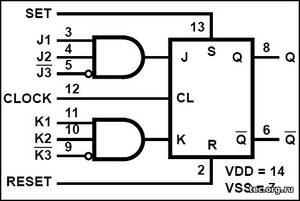

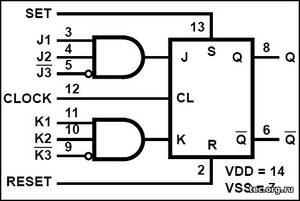

Расположение выводов м/с 4096:

|

Назначение выводов м/с 4096:

|

1

|

NC |

не подключен |

|

2

|

RESET |

Сброс (установка 0) асинхронный |

|

3

|

J1 |

Входы установки J

объединенные по "И" |

|

4

|

J2 |

|

5

|

__

J3 |

|

6

|

_

Q |

Выход инверсный |

|

7

|

Vss |

Общий (Gnd) |

|

8

|

Q |

Выход прямой

|

| 9 |

__

K3 |

Входы установки K

объединенные по "И" |

| 10 |

K2 |

| 11 |

K1 |

| 12 |

CLOCK |

Тактовый вход |

| 13 |

SET |

Установка 1 асинхронная |

| 14 |

Vdd |

Питание (+U) |

|

|

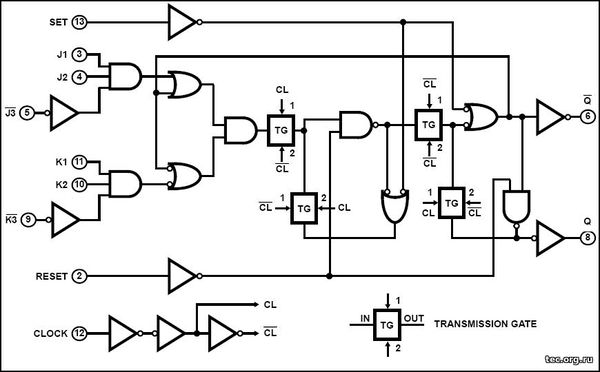

Микросхема MMC4096E представляет собой классический JK-триггер с синхронными (J и K) и асинхронными (S и R) входами установки и сброса. Триггер двухступенчатый типа "Master-Slave". При этом синхронные входы установки J1,J2,J3 и K1,K2,K3 объединены по три схемами "И". при этом, в отличие от микросхемы 4095, входы J3 и K3 имеют инверсию сигнала. В дальнейшем рассматриваются результатирующие сигналы J и K (см. упрощенную функциональную схему).

Логическая "1" со входов J или K транслируется на прямой или инверсный выходы Q соответственно при положительном перепаде уровня на тактовом входе CLOCK. В остальное время осуществляется хранение в триггере ранее поступившей информации.

Если на обоих входах J и K высокий уровень сигнала в момент прихода тактового импульса, то состояние выхода триггера инвертируется. Таким образом образуется T-триггер (счётный).

Входы SET и RESET асинхронные. По умолчанию на них должны быть низкие уровни напряжения. При поступлении сигнала высокого уровня на SET выход Q переходит также в состояние высокого уровня, а при поступлении высокого уровня на RESET выход Q сбрасывается в 0. Это происходит вне зависимости от сигналов на входах J, K и CLOCK.

|

Упрощенная функциональная схема м/с 4096:

_ _

J=J1*J2*J3 K=K1*K2*K3 |

Таблица функционирования м/с 4096:

CLOCK |

J |

K |

SET |

RESET |

Q |

_

Q |

X |

0 |

0 |

0 |

0 |

Qn-1 |

___

Qn-1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

___

Qn-1 |

Qn-1 |

|

X |

X |

0 |

1 |

0 |

1 |

|

X |

X |

1 |

0 |

1 |

0 |

|

X |

X |

1 |

1 |

0 |

0 |

|

X |

X |

|

|

Qn-1 |

___

Qn-1 |

0 - низкий уровень, 1 - высокий уровень,

X - произвольное состояние

Qn-1 - предыдущее состояние выхода

|

|

Структурная схема микросхемы 4096:

(нажмите для увеличения)

|

|

Более подробные параметры микросхемы MMC4096E с динамическими характеристиками и диаграммами работы Вы можете получить скачав файл документации ниже (Datasheet на английском языке).

|

|

[ Скачать документацию на 4096 (MMC4096E)  (157.6 Kb) ] (157.6 Kb) ]

|

Производитель: Microelectronica

|

ЦЕНА розничная: 15руб | от 10шт: 10руб | от 100шт: 5руб | Код товара: 6101 |

|

| Просмотров: 2583

|

|

|