|

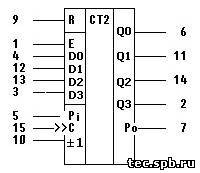

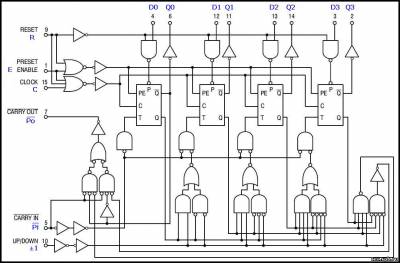

Счётчик К561ИЕ11 удобно применять для подсчета приращения данных, причем несколько микросхем К561ИЕ11 можно объединить в многокаскадные синхронные либо асинхронные счетчики. На основе этих микросхем выполняются синхронные делители частоты. Счетчик имеет четыре выхода Q0-Q3, входы предварительной записи данных (установки) D0-D3, а также вход E разрешения этой операции. Вход и выход переноса Pi и Po имеют активные напряжения низкого уровня.

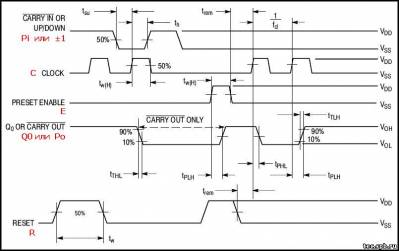

Запускающий тактовый перепад на входе С для счетчика К561ИЕ11 - положительный. Для переключения направления счета (на увеличение или на уменьшение) служит вход ±1. При высоком уровне на этом входе производится сложение тактовых импульсов на входе C с содержимым регистров счётчика, при низком уровне - вычитание.

Вход сброса данных R - асинхронный - он имеет абсолютный приоритет по отношению к любому другому входу. Все разряды счётчика сбрасываются в ноль, если на вход R подается напряжение высокого уровня.

Синхронное каскадирование счетчиков К561ИЕ11 получится, если соединить параллельно тактовые входы и подать сигнал от выхода переноса Po первого счетчика на вход переноса Pi последующего (более старшего). Для асинхронного каскадирования требуется соединить Po с тактовым входом С последующей микросхемы. Вход Pi первого (или единственного) счётчика соединяют с общим проводом.

|